# **DATA SHEET**

# NVIDIA Jetson AGX Xavier Series System-on-Module

Volta GPU + Carmel CPU + LPDDR4x + eMMC

# **NVIDIA Jetson AGX Xavier Modules:**

| Module                              | Description                                                                   |

|-------------------------------------|-------------------------------------------------------------------------------|

| Jetson AGX Xavier (JAX)             | Volta GPU + Carmel CPU + 32 GB LPDDR4x + 32 GB eMMc                           |

| Jetson AGX Xavier 64GB (JAX 64GB)   | Volta GPU + Carmel CPU + 64 GB LPDDR4x + 32 GB eMMc                           |

| Jetson AGX Xavier Industrial (JAXi) | Volta GPU + Carmel CPU + 32 GB LPDDR4x (ECC support) + 64 GB eMMC + 64 MB NOR |

References to JAX include (can be read as) JAX 64GB and JAXi except where explicitly noted.

### **Volta GPU**

OpenGL<sup>®</sup> 4.6 | OpenGL ES 3.2 | Vulkan<sup>™</sup> 1.0 | CUDA<sup>®</sup> 10

# **Carmel CPU Complex**

ARMv8.2 (64-bit) heterogeneous multi-processing (HMP) CPU architecture | dual-core CPU clusters connected by a highperformance system coherency interconnect fabric | L3 Cache: Three multi-mode (eDP/DP/HDMI) Serial Output Resources 4MB (shared across all clusters)

NVIDIA Carmel (Dual-Core) Processor: L1 Cache: 128KB L1 instruction cache (I-cache) per core; 64KB L1 data cache (Dcache) per core | L2 Unified Cache: 2MB per cluster

# **Audio Subsystem**

Dedicated programmable audio processor | ARM Cortex A9 with NEON | 12S outputs: 4x (JAX, JAX 64GB), **3x (JAXi)** | 2 x I and Q baseband data channels | PDM in/out | Industrystandard High Definition Audio (HDA) controller provides a multi-channel audio path to the HDMI interface.

### Memory

256-bit DRAM interface | Secure External Memory Access Using TrustZone Technology | System MMU | ECC (enabled by software for JAXi only) | Memory Type: LPDDR4x | Memory Size: 64GB (JAX 64GB); 32GB (JAX, JAXi)

### Storage

eMMC 5.1 Flash Storage | Bus Width: 8-bit | Maximum Bus Frequency: 200MHz (HS400) | Storage Capacity: 32GB (JAX, JAX 64GB);64GB (JAXi)

QSPI NOR Flash Storage (JAXi Only) Bus Width: 32-bit Maximum Bus Frequency: 65MHz | Storage Capacity:64MB (JAXi)

### **Networking**

10/100/1000 BASE-T Ethernet | Media Access Controller (MAC) | **RGMII Interface**

### **Imaging**

Tensor Cores | End-to-end lossless compression | Tile Caching | 16 lanes (supporting up to 4x4, 6x2, 6x1 configurations) | MIPI CSI-2 | D-PHY 1.2 (up to 2.5Gb/s per lane, total bandwidth up to 40 Gbps) | C-PHY 1.1 (1.7Gsym/s per trio, total bandwidth up to 62 Gbps)

### **Display Controller Subsystem**

(SOR) | HDMI 2.0a/b (up to 6Gbps), DP 1.4, eDP 1.4 (up to 5.4Gbps) | HDCP 1.4 and 2.2.

Maximum Resolution (DP/eDP/HDMI): (up to) 3840x2160 at 60Hz (up to 36 bpp)

### Multi-Stream HD Video & JPEG

Video Encode: H.265 (HEVC), H.264, VP9

Video Decode: H.265 (HEVC), H.264, VP9, VP8, MPEG-4, MPEG-2, VC-1

JPEG (Decode & Encode)

### **Peripherial Interfaces**

USB: xHCI host controller with integrated PHY (up to) 3 x USB 3.1, 4 x USB 2.0; USB 3.0 device controller with integrated PHY PCIe: x8, x4, x2, (2x) x1 | SD/MMC controller (supporting eMMC 5.1, SD 4.0, SDHOST 4.0 and SDIO 3.0) | 5x UART | 3 x SPI | 5 x 12C | 2 x CAN | GPIOs.

### Mechanical

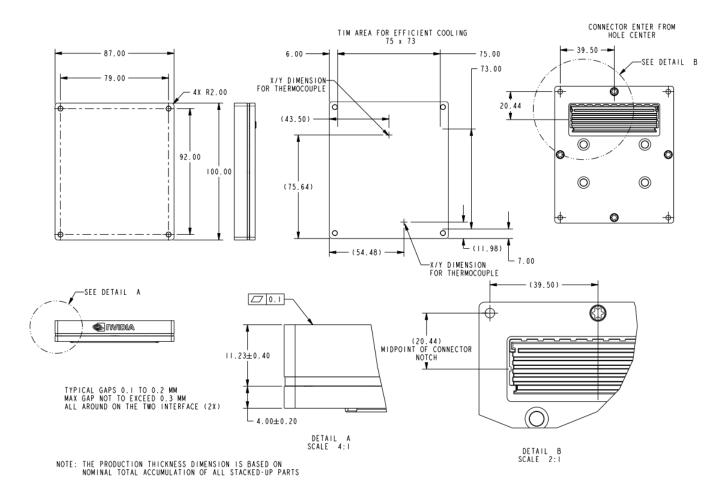

Module Size: 100 mm x 87 mm | PCB: 12L ELIC HDI | Connector: 699 pin B2B connector | Integrated Thermal Transfer Plate (TTP) with Heatpipe.

### **Operating Requirements**

Temperature Range: -25C - 80C (JAX, JAX 64GB); -40C - 85C (JAXi) | Maximum Module Power: 30W (JAX, JAX 64GB); 40W (JAXi) Power Input: System Voltage Input 9.0V – 20.0V; 5V Input: 5.0V | Operating Lifetime (24x7): 5 years (JAX, JAX 64GB); 10 years (JAXi)

Refer to the documentation provided with each software release for additional information on current software support.

# **Revision History**

| Version | Date              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.3     | November 25, 2020 | Initial release including information for Jetson AGX Xavier Industrial.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 1.4     | January 12, 2021  | Introduced JAX and JAXi abbreviations for Jetson AGX Xavier and Jetson AGX Xavier Industrial, respectively.  Memory Subsystem: Corrected LPDDR4x Memory Bus Table. Table incorrectly listed a 64GB memory size for JAXi This was corrected to 32GB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 1.5     | June 11, 2021     | Description  Audio Subsystem: updated number of I2S outputs for JAXi Memory: updated to include ECC support for JAXi Imaging: added description of CSI interface Peripherial Interfaces: updated number of UART interfaces for JAXi Operating Requirements: updated to include Operating Lifetime, updated Temperature Range and Maximum Module Power for JAXi  Functional Description Added Programmable Computer-Vision Accelerator (PVA) description Added Safety Cluster Engine (SCE) description  Volta GPU: Updated JAXi GPU operating frequency  Carmel CPU Complex: Updated JAXi CPU operating frequency  Memory Subsystem: Updated to include ECC support for JAXi High Definition (HD) Audio/Video Subsystem  Multi-Standard Video Decoder: updated Supported Video Decoder Standards for JAXi Multi-Standard Video Encoder: updated Supported Video Encoder Standards for JAXi  Power and System Management  VCC_RTC: updated to include current draw for backup cell Power Sequencing: removed Power Sequencing Diagrams, Refer to the Jetson AGX Xavier Series Module Product Design Guide for this information.  Absolute Maximum Ratings: Updated Max Operating and Storage temperatures for JAXi Environmental & Mechanical Screening: Updated JAXi Testing table to include MTBF information |

| 1.6     | December 03, 2021 | Package Drawing and Dimensions: Updated Module Outline Drawing  Module Marking: Updated Module Marking for JAXi  Updated to include support for Jetson AGX Xavier 64GB (JAX 64GB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|         |                   | Pin List: Updated pin list  Environmental & Mechanical Screening: Updated JAXi Testing table to include Ground Mobile (GM) MTBF information  Module Marking: Added Module Marking for JAX 64GB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1.7     | January 27, 2022  | DC Characteristics  • I/O pin voltage clarification; updated VDD references to VDDIO where voltage was associated with a given I/O pin; VM_PIN, Digital Logic DC Characteristics.  • Included information on how to determine corresponding voltage (VDDIO) for the desired pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Version | Date            | Description                                                                                                                                                                                                                                                                                                                                            |

|---------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.8     | August 18, 2022 | <ul> <li>VCC_RTC: added RTC accuracy; moved current requirements to Recommended Operating Conditions table.</li> <li>Physical / Electrical Characteristics</li> <li>Recommended Operating Conditions: updated VCC_RTC; JAX current requirements moved here, updated to include JAXi requirements, JAXi VCC_RTC input updated to 2.25-5.5 V.</li> </ul> |

# Table of Contents

| 1              | Functional Description                                                                                            | 8  |

|----------------|-------------------------------------------------------------------------------------------------------------------|----|

| 1.1            | Volta GPU                                                                                                         | 8  |

| 1.2            | Carmel CPU Complex                                                                                                | 10 |

| 1.3            | Memory Subsystem                                                                                                  | 11 |

| 1.4            | Video Input                                                                                                       | 12 |

|                | MIPI Camera Serial Interface (CSI)                                                                                | 13 |

|                | Image Signal Processor                                                                                            |    |

| 1.5            | Display Controller                                                                                                | 14 |

| 1.5.1<br>1.5.2 | High-Definition Multimedia Interface (HDMI) and DisplayPort (DP) Interfaces  Embedded DisplayPort (eDP) Interface |    |

| 1.6            | High Definition (HD) Audio/Video Subsystem                                                                        | 17 |

| 1.6.2          | Multi-Standard Video Encoder                                                                                      | 18 |

|                | Video Image Compositor                                                                                            |    |

|                | Audio Processing Engine                                                                                           |    |

| 1.7            | Security                                                                                                          | 26 |

|                |                                                                                                                   |    |

| 1.8            | Vision Accelerator                                                                                                | 27 |

| 1.9            | Deep Learning Accelerator                                                                                         | 28 |

| 1.10           | Safety Cluster Engine                                                                                             | 29 |

| 1.11           | Interface Descriptions                                                                                            | 29 |

|                | L SD/eMMC Controller                                                                                              |    |

| 1.11.3         | 2 Universal Flash Storage Complex                                                                                 | 30 |

| 1 11 4         | 1 PCIA                                                                                                            | 21 |

| Serial Peripheral Interface (SPI)                         | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Quad Serial Peripheral Interface Controller - (JAXi only) | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Universal Asynchronous Receiver/Transmitter (UART)        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Reduced Gigabit Media Independent Interface (RGMII)       | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Power and System Management                               | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| VCC_RTC                                                   | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Power Sequencing                                          | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

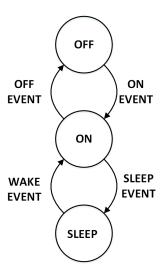

| Power States                                              | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| ON State                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SLEEP State                                               | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Pin Definitions                                           | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Power-on Reset Behavior                                   | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Deep Sleep Behavior                                       | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Pin List                                                  | 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Physical / Flectrical Characteristics                     | 81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Absolute Maximum Ratings                                  | 81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Recommended Operating Conditions                          | 82                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Digital Logic                                             | 82                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Environmental & Mechanical Screening                      | 83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Package Drawings and Dimensions                           | 87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

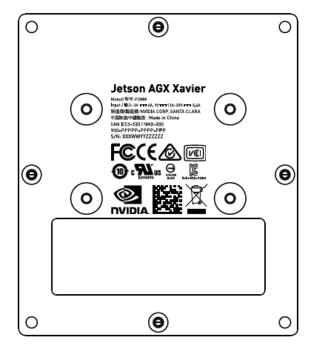

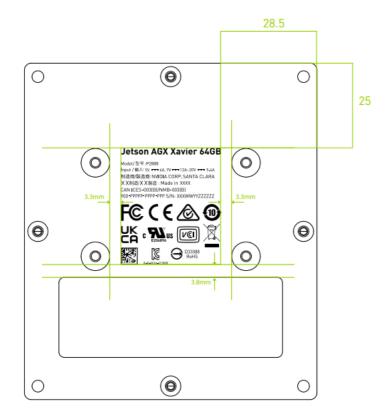

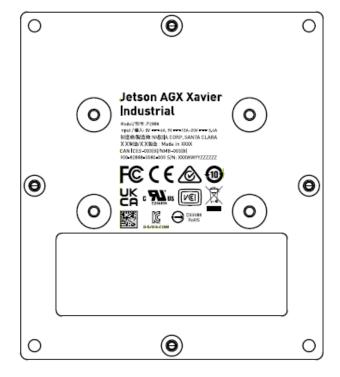

| Module Marking                                            | 89                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                           | Quad Serial Peripheral Interface Controller - (JAXi only) Universal Asynchronous Receiver/Transmitter (UART) Controller Area Network (CAN) Reduced Gigabit Media Independent Interface (RGMII)  Power and System Management  VCC_RTC  Power Sequencing  Power States  ON State  OFF State SLEEP State  Pin Definitions  Power-on Reset Behavior  Deep Sleep Behavior  Pin List  Physical / Electrical Characteristics  Absolute Maximum Ratings  Recommended Operating Conditions  Digital Logic  Environmental & Mechanical Screening  Package Drawings and Dimensions |

# 1 Functional Description

The Jetson AGX Xavier (JAX) series module is a high performance, small-form factor device. It enables modular system design by mechanically isolating integrated components from external mechanical forces, standardizing thermal and mechanical interfaces, and exposing a comprehensive set of system and peripheral interfaces at the 699-pin board-to-board connector. JAX series module can be used in a wide variety of applications requiring varying performance metrics. To accommodate these varying conditions, JAX series modules implement a multi-tiered solution that focuses on the efficient application of performance as a means to manage a complex environment:

- Power Management Controller (PMC): The PMC primarily controls voltage transitions for the Xavier SoC as it transitions to/from different low power modes; it also acts as a slave receiving dedicated power/clock request signals as well as wake event from dedicated GPIO which can wake the module from a deep sleep state.

- **Power Gating**: JAX series modules aggressively employ power-gating (controlled by the PMC) to power-off blocks which are idle. CPU cores are on a separate power rail to allow complete removal of power and eliminate leakage. Each CPU can be power gated independently internally. Software provides context save/restore to/from DRAM.

- Clock Gating: Used to further reduce unnecessary power consumption where power gating is not an option.

- **Dynamic Voltage and Frequency Scaling (DVFS)**: Raises voltages and clock frequencies when demand requires, Lowers them when less is sufficient, and removes them when none is needed. DVFS is used to change the voltage and frequencies on the following rails: VDD\_CPU0, VDD\_CPU1, VDD\_GPU, and VDD\_CV.

- **Real Time Clock (RTC)**: The RTC Always On partition logic of the CPU Complex is not power gated and can wake the system based on either a timer event or an external trigger (e.g., key press).

JAX series modules have two power inputs: 1) a 5V Regulator input and 2) a 9V - 20V input. Power is then supplied to the devices on board through a power management IC (PMIC) and dedicated voltage regulators; all internal module voltages and IO voltages are generated from this input. An optional back up battery can be attached to the VCC\_RTC module input (this will maintain the on system RTC, when VIN is not present). VIN must be supplied by the carrier board that the JAX module is designed to connect to.

# 1.1 Volta GPU

The same Volta GPU architecture that powers NVIDIA high-performance computing (HPC) products was adapted for use in JAX series modules. The Volta architecture features a new Streaming Multiprocessor (SM) optimized for deep learning. The new Volta SM is far more energy efficient than the previous generations enabling major performance boosts in the same power envelope. The Volta SM includes:

- New programmable Tensor Cores purpose-built for INT8/FP16/FP32 deep learning tensor operations; IMMA and HMMA instructions accelerate integer and mixed-precision matrix-multiply-and-accumulate operations.

- Enhanced L1 data cache for higher performance and lower latency.

- Streamlined instruction set for simpler decoding and reduced instruction latencies.

- Higher clocks and higher power efficiency.

The Volta architecture also incorporates a new generation of its memory subsystem and enhanced unified memory and address translation services that increases memory bandwidth and improves utilization for greater efficiency.

The Graphics Processing Cluster (GPC) is a dedicated hardware block for compute, rasterization, shading, and texturing; most of the GPU's core graphics functions are performed inside the GPC. It is comprised of Texture Processing Clusters (TPC), with each TPC containing two SM units, and a Raster Engine. The SM unit creates, manages, schedules and executes instructions from many threads in parallel. Raster operators (ROPs) continue to be aligned with L2 cache slices and memory controllers. The SM geometry and pixel processing performance make it highly suitable for rendering advanced user interfaces; the efficiency of the Volta GPU enables this performance on devices with power-limited environments.

Each SM is partitioned into four separate processing blocks (referred to as SMPs), each SMP contains its own instruction buffer, scheduler, CUDA cores and Tensor cores. Inside each SMP, CUDA cores perform pixel/vertex/geometry shading and physics/compute calculations, and each Tensor core provides a 4x4x4 matrix processing array to perform mixed-precision fused multiply-add (FMA) mathematical operations. Texture units perform texture filtering and load/store units fetch and save data

to memory. Special Function Units (SFUs) handle transcendental and graphics interpolation instructions. Finally, the PolyMorph Engine handles vertex fetch, tessellation, viewport transform, attribute setup, and stream output.

# Table 1 GPU Operation

| Module        | GPC Configuration |               |                 | Performance (peak)  | Operating Frequency per Core (up to) |

|---------------|-------------------|---------------|-----------------|---------------------|--------------------------------------|

|               | Number<br>of TPC  | CUDA<br>Cores | Tensor<br>Cores |                     |                                      |

| JAX, JAX 64GB | 4                 | 512           | 64              | 10 TFLOPS   32 TOPS | 1.37 GHz                             |

| JAXi          | 4                 | 512           | 64              | 10 TFLOPS   30 TOPS | 1.21 GHz                             |

#### Features:

- End-to-end lossless compression

- Tile Caching

- OpenGL 4.6, OpenGL ES 3.2, and Vulkan 1.0

#### Note

Product is based on a published Khronos Specification and is expected to pass the Khronos Conformance Process. Current conformance status can be found at <a href="https://www.khronos.org/conformance">www.khronos.org/conformance</a>.

- Adaptive Scalable Texture Compression (ATSC) LDR profile supported

- DirectX 12 compliant

- CUDA support

- Iterated blend, ROP OpenGL-ES blend modes

- 2D BLIT from 3D class avoids channel switch

- 2D color compression

- Constant color render SM bypass

- 2x, 4x, 8x MSAA with color and Z compression

- Non-power-of-2 and 3D textures, FP16 texture filtering

- FP16 shader support

- Geometry and Vertex attribute Instancing

- Parallel pixel processing

- Early-z reject: Fast rejection of occluded pixels acts as multiplier on pixel shader and texture performance while saving power and bandwidth

- Video protection region

- Power saving: Multiple levels of clock gating for linear scaling of power

# 1.2 Carmel CPU Complex

The CPU complex (CCPLEX) is comprised of Carmel dual-core CPU clusters in a coherent multi-processor configuration. A high-performance System Coherency Fabric (SCF) connects all CPU clusters enabling simultaneous operation of all CPU cores (as needed) for a true heterogeneous multi-processing (HMP) environment. The SCF also connects CPU clusters to:

- DRAM through the Memory Controller Fabric (MCF).

- Other processing and I/O blocks in the Memory Mapped I/O (MMIO) space through an ARM Advanced eXtensible Interface (AXI).

Each CPU cluster contains two identical Carmel processors; each core includes 128 KB Instruction (I-cache) and 64 KB Data (D-cache) Level 1 caches, a 2 MB L2 cache is shared by both cores.

### Table 2 CPU Operation

| Module        | CPU Configuration             | tion |     |   | Operating Frequency<br>per Core (up to) * |

|---------------|-------------------------------|------|-----|---|-------------------------------------------|

|               | CPU Cluster L2 Cache L3 Cache |      |     |   |                                           |

| JAX, JAX 64GB | 4 x dual-core                 | 8MB  | 4MB | 8 | 2.26Ghz                                   |

| JAXi          | 4 x dual-core                 | 8MB  | 4MB | 8 | 2.03GHz                                   |

<sup>\*</sup> Refer to the documentation provided with each software release for additional information on supported power modes and CPU operation.

- NVIDIA Dynamic Code Optimization

- 10-wide Superscalar architecture

- Dynamic branch prediction with a Branch Target Buffer and Global History Buffer RAMs, a return stack buffer, and an indirect predictor.

- Full implementation of ARMv8.2 ISA compliant architecture including:

- ARMv8 TrustZone

- ARMv8.0 Crypto ISA

- Trusted Memory

- TZ-RAM

- TZ-DRAM

- Dynamic CMA VPR

- GSC DRAM Carveouts

- Clock Monitoring

- Voltage Monitoring

- Trusted Boot

- Trusted Debug

- ARMv8.2-FP16 support

- 128 KB 4-way-associative parity protected L1 instruction cache per core

- 64 KB 4-way-associative parity protected L1 data cache per core

- 2 MB 16-way-associative ECC protected L2 cache per CPU cluster

- 4 MB 16-way-associative ECC protected L3 cache (shared across all clusters)

- Performance Monitoring

- Interface to an external Generic Interrupt Controller (vGIC-400)

- Support for power management with multiple power domains

# 1.3 Memory Subsystem

The Memory Subsystem (MSS) provides access to local DRAM, SysRAM, and provides a SyncPoint Interface for inter-processor signaling. The memory subsystem supports full-speed I/O coherence by routing requests through a scalable coherence fabric. It also supports a comprehensive set of safety and security mechanisms.

Structurally, the MSS consists of:

- 1. MSS Data Backbone routes requests from clients to the MSS Hub and responses from MSS Hub to the clients.

- 2. MSS Hub receives and arbitrates among client requests, performs SMMU translation, and sends requests to the MCF.

- 3. Memory Controller Fabric (MCF) performs security checks, feeds I/O coherent requests to the Scalable Coherence Fabric (SCF), and directs requests to the multiple memory channels.

- 4. Memory Controller (MC) Channels row sorter/arbiter and DRAM controllers.

- 5. DRAM IO channel-to-pad fabric, DRAM I/O pads, and PLLs.

JAX series modules integrate a 256-bit wide LPDDR4X memory interface implemented as eight 32-bit channels with x16 subpartitions. The memory controller provides a single read or write command and row address to both sub-partitions in the channel to transfer 64 bytes, but provides three independent column address bits to each sub-partition, allowing it access different 32 byte sectors of a GOB between the sub-partitions. It provides connections between a wide variety of clients, supporting their bandwidth, latency, quality-of-service needs and any special ordering requirements that are needed. The MSS supports a variety of security and safety features and address translation for clients that use virtual addresses.

### Table 3 LPDDR4x Memory Bus

| Module   | Size | Maximum Bandwidth | Maximum Bus Frequency | ECC Support               |

|----------|------|-------------------|-----------------------|---------------------------|

| JAX      | 32GB | 136.5GB/s         | 2133MHz               | No                        |

| JAX 64GB | 64GB | 136.5GB/s         | 2133MHz               | No                        |

| JAXi     | 32GB | 136.5GB/s         | 2133MHz               | Yes (enabled by software) |

- LPDDR4X: x32 DRAM chips

- 256-bit wide data bus

- Low Latency Path and Fast Read/Response Path Support for the CPU Complex Cluster

- Support for low-power modes:

- Software controllable entry/exit from: self-refresh, power down, deep power down

- Hardware dynamic entry/exit from: power down, self-refresh

- Pads use DPD-mode during idle periods

- · High-bandwidth interface to the integrated Volta GPU

- Full-speed IO coherence with bypass for Isochronous (ISO) traffic

- System Memory-Management Unit (SMMU) for address translation based on the ARM SMMU-500

- · High-bandwidth PCIe ordered writes

- · AES-XTS encryption with 128-bit key

- DRAM ECC (Enabled by software for JAXi only)

- SEC (Single Error Correction)

- DED (Double Error Detection)

- Parity protection support

# 1.4 Video Input

JAX series modules incorporate support for both the MIPI Camera Serial Interface (CSI) and Sony's Scalable Low Voltage Signaling with Embedded Clock (SLVS-EC) interface. Both interfaces work with the Video Input (VI) block to capture an image from a sensor, where NVCSI/SLVS-EC are sources of pixel data to VI. Image capture interfaces work in streaming mode while VI captures the required frames using a single-shot mode of operation. All sync point generation for software is handled at VI; the delay between image capture and VI is negligible in software terms. Image capture interfaces do not have a direct memory port, instead they send the pixel data to memory through VI.

Camera data input interfaces supported: CSI-2 and SLVS-EC v1.2; pixels are already decoded and aligned by the external CSI or SLVS-EC units.

#### Note

SLVS-EC not supported on JAXi modules

# 1.4.1 MIPI Camera Serial Interface (CSI)

| Standard                                                                                            | Notes                                                        |

|-----------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| MIPI Alliance Specification for Camera Serial Interface 2 (CSI-2), version 2.0, MIPI Alliance, Inc. | Not Supported:  Camera Controller Interface (CCI) Predictor2 |

| MIPI Alliance Specification for C-PHY, version 1.1, MIPI Alliance, Inc.                             |                                                              |

| MIPI Alliance Specification for D-PHY, version 1.2, MIPI Alliance, Inc.                             |                                                              |

Fifth-generation NVIDIA camera solution (NVCSI 2.0, VI 5.0, and ISP 5.0) provides a combination host that supports both MIPI C-PHY and enhanced MIPI D-PHY (with lane deskew support) physical layer options in four 4-lane, six 2-lane, or six 1-lane configurations; or combinations of these. Each lane can support up to 16 virtual channels (VC) and supports data type interleaving.

- Virtual Channel Interleaving: VCs are defined in the CSI-2 specification and are useful when supporting multiple camera sensors. With the VC capability, a one-pixel parser (PP) can de-interleave up to 16 image streams.

- Data Type Interleaving: In HDR line-by-line mode, the sensor can output long/short exposure lines using the same VC and a different programmable data type (DT).

- Frequency Target: The parallel pixel processing rate, measured in pixels-per-clock (PPC), is increased to allow higher throughput and lower clock speeds. To support higher bandwidth without increasing the operating frequency, the host processes multiple pixels in one clock. NVCSI is capable of processing four PPCs when bits-per-pixel (BPP) is greater than 16, and eight PPC when BPP is less than or equal to 16.

- With the new streaming mode in NVCSI, one PP can handle all traffic (embedded data and image data) from one camera device, including 16 VCs.

- Supports both the MIPI D-PHY v1.2 and the MIPI C-PHY v1.1 physical layer options.

- MIPI D-PHY supports up to 2.5 Gbits/sec per pair, for an aggregate bandwidth of 40 Gbps from 16 pairs

- MIPI C-PHY supports up to 1.7 G symbol/sec (Gsym/s) per trio

- Based on MIPI CSI-2 v2.0 protocol stack

- Includes six pixel parsers (PP)

- Supports up to 16 virtual channels (VC) per active PP

- Supported input data formats:

- RGB: RGB888, RGB666, RGB565, RGB555, RGB444

- YUV: YUV422-8b, YUV420-8b (legacy), YUV420-8b, YUV444-8b

- ° RAW: RAW6, RAW7, RAW8, RAW10, RAW12, RAW14, RAW16, RAW20

- DPCM (predictor 1): 14-10-14, 14-8-14, 12-8-12, 12-7-12, 12-6-12, 12-10-12, 10-8-10, 10-7-10, 10-6-10

- Data type interleave support

# 1.4.2 Scalable Low Voltage Signaling with Embedded Clock (SLVS-EC) - (JAX, JAX 64GB only)

#### Note

Not supported on JAXi modules

| Standard                                                                        | Notes |

|---------------------------------------------------------------------------------|-------|

| Scalable Low Voltage Signaling with Embedded Clock (SLVS-EC) Specification v1.2 |       |

SLVS-EC sensors operating in slave mode require the JAX series module to send out a vertical sync signal (XVS) and horizontal sync signal (XHS). The on-board SLVS-EC timing generator (i.e., VI sync generator – SYNCGEN) produces these signals using a fractional-rate divider and drives them to the sensor.

#### Features:

- Sensor slave mode, shared clock

- Up to 8 lanes

- Up to 2 streams

- Mode change with standby

- 1152 Mbps and 2304 Mbps baud rate

- Supported input data formats:

- RAW8, RAW10, RAW12, RAW14, RAW16 formats

- Packet footer CRC

- 2 data ID

# 1.4.3 Video Input (VI) Block

The Video Input (VI) block receives data from the CSI receiver and prepares it for presentation to system memory or the dedicated image signal processor (ISP) execution resources. The VI block provides formatting for RGB, YCbCr, and raw Bayer data in support of a number of camera user models. These models include single and multi-camera systems, which may have up to six active streams. The input streams are obtained from MIPI compliant CMOS sensor camera modules.

# 1.4.4 Image Signal Processor

The Image Signal Processor (ISP) takes data from the VI or CSI block in raw Bayer format and processes it to YUV output. Advanced image processing is used to convert input to YUV data, and remove artifacts introduced by high-megapixel CMOS sensors, camera lens, and color-space conversion.

- CSI Virtual Channel (VC) supports four VCs per CSI x4 brick

- Local Tone Map

- Bayer Histogram statistics for auto-exposure

- Bayer average map for auto white balance and auto-exposure

- Sharpness map for auto focus

- Parity Protection

- Bad pixel count

- Deadlock detection

# 1.5 Display Controller

The JAX series module integrates a unified display controller (based on the NVIDIA NVDisplay architecture) and three independent display outputs. The Display Controller includes a Pixel Processing Engine that fetches pixel data to be processed from DRAM and generates up to six windows of rasterized display-ready pixel data. The instructions for processing the pixel data are captured by the display controller's Front End (FE) logic, which then generates the individual controls for the various stages of pixel processing. The pixel data to be processed are fetched in the Isochronous Memory Hub (IsoHub) then go through the specified pixel processing, including merging the cursor, in four pipe stages: Pre-Composition (Pre-comp); Composition (Comp); Post-Composition (Post-comp); and Raster Generation (RG). The rasterized display-ready pixel data are available for the separate panels/devices (referred to as display heads) and are fed through a multi-channel crossbar structure to the Serial Output Resources (SOR) in the Display Interface for the standard display output format, i.e. DP (Display Port) and HDMI (High Definition Multimedia Interface).

Each of the display heads can be run at an independent clock rate, and each can drive a different display resolution. Each of the six display windows (A, B, C, D, E, F) can be arbitrarily assigned to any of the display Heads as required, then connected to any one of the display heads for desired output format.

- Integrated HDCP key storage, no external SecureROM required

- Six windows that can be assigned to any Head

- One special-purpose TrustZone protected window on Head0

- Maximum raster size: 32768 x 32768

- Maximum active region: 8192 x 8192

- Maximum input surface size: 32768 x 32768

- Maximum fetched size: 8192 x 8192

- Input surface color formats:

- 16-bit RGB: R4G4B4A4, R5G6B5, A1R5G5B5, and R5G5B5A1

- 24-bit RGB: A8R8G8B8, X8R8G8B8, A8B8G8R8, and X8B8G8R8

- 32-bit RGB: A2R10G10B10, A2B10G10R10, X2BL10GL10RL10\_XRBIAS, and X2BL10GL10RL10\_XVYCC

- 64-bit RGB: R16 G16 B16 A16 NVBIAS, and R16 G16 B16 A16

- Packed YUV 422: Y8 U8 Y8 V8 N422, and U8 Y8 V8 Y8 N422

- Semi Planar YUV 422 (8, 10, 12 bpc):

- Y8 V8U8 N422, Y8 V8U8 N422R

- Y10 V10U10 N422, Y10 V10U10 N422R

- Y12\_V12U12\_N422, Y12\_V12U12\_N422R

- Semi-planar YUV 420 (8, 10, 12 bpc):

- Y8\_V8U8\_N420\*

- Y10\_V10U10\_N420\*

- Y12 V12U12 N420\*

- Semi-planar YUV 444 (8, 10, 12 bpc):

- Y8\_V8U8\_N444

- Y10\_V10U10\_N444

- Y12\_V12U12\_N444

- Planar YUV 420 (8, 10, 12 bpc):

- Y8\_U8\_V8\_N420

- Y10\_U10\_V10\_N420

- Y12\_U12\_V12\_N420

- Planar YUV 444 (8, 10, 12 bpc):

- Y8\_U8\_V8\_N444

- Y10\_U10\_V10\_N444

- Y12 U12 V12 N444

- Pipeline depth

- 16-bpc, [-1.5, 2.5] range (two range extension bits): De-gamma will clip to 0,1 immediately on the input

- Vsync (VCOUNTER) and immediate (HCOUNTER) flip modes

- Immediate flip supported for RGB only

- Immediate flips occur at the second 8-line boundary after the current line.

### Note

- Cursor cannot be enabled on a Head unless the Head has at least one window group attached. The window group does not need to be enabled.

- TrustZone cannot be enabled unless Head0 has at least one window group attached. This does not need to be enabled.

- Color formats marked with an asterisk (\*) are programmed as Y\_UV in the display manuals, and then byte-swapped later to be Y\_VU.

- 10-bpc and 12-bpc YUV color formats are packed into 16-bpc containers. This effectively limits immediate flips to no faster than one every 16 lines.

# 1.5.1 High-Definition Multimedia Interface (HDMI) and DisplayPort (DP) Interfaces

| Standard                                                                  | Notes                                                                                  |

|---------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| High-Definition Multimedia Interface (HDMI) Specification, version 2.0a/b | > 340 MHz pixel clock<br>Scrambling support<br>Clock/4 support (1/40 bit-rate clock)   |

| VESA DisplayPort Standard Version 1.4                                     |                                                                                        |

| HDMI <sup>®</sup> Specification 2.0                                       | HDMI 1.4 (up to 340 MHz pixel clock rate)<br>HDMI 2.0 (up to 594 MHz pixel clock rate) |

A standard DP 1.4 or HDMI 2.0a/b interface is supported. These share the same set of interface pins, so either DisplayPort or HDMI can be supported natively. Dual-Mode DisplayPort (DP++) can be supported, in which the DisplayPort connector logically outputs TMDS signaling to a DP-to-HDMI dongle. Each output collects the output of a display pipeline from the display controller, formats/encodes that output (to a desired format), and then streams it to an output device. Each output is capable of providing an interface to an external device; each output can drive only a single output device at any given time. HDMI support provides a method of transferring both audio and video data; the SOR receives video from the display controller and audio from a separate high-definition audio (HDA) controller, it combines and transmits them as appropriate.

### Note

A single CEC controller is shared between HDMI and DP interfaces and can only be applied for use on one interface (i.e., does not support multiple instances if both interfaces were used for HDMI).

#### **Features:**

- DisplayPort

- (up to) 540MHz pixel clock rate (i.e., 1.62GHz for RBR, 2.7GHz for HBR, and 5.4GHz for HBR2).

- 8b/10b encoding support

- External Dual Mode standard support

- Audio streaming support

- HDMI

- (up to) 594 MHz pixel clock

- 8/12 bpc RGB and YUV444

- 8/10/12 bpc YUV422

- 8 bpc YUV420 (10/12 bpc YUV frame buffers should be output as YUV422)

- HDMI Vendor-Specific Infoframe (VSI) packet transmission

- On HDMI, multichannel audio from HDA controller, up to 8 channels, 192 KHz, 24-bit.

- Fuse calibration information for HDMI analog parameter(s)

- 1080i output on HDMI

- DP or HDMI connectors via appropriate external level shifting

- HDCP 2.2 and 1.4 over either DP or HDMI

- External Dual Mode standard (DP2HDMI passive or active adapters and adapter discovery)

- Generic infoframe transmission

- Frame-packed 3D stereo mode

- Safety based on Register Parity

#### Note

\* (Resolution + Refresh Rate + Pixel Depth + Format) must be within specification limits to achieve support for desired pixel depth.

# 1.5.2 Embedded DisplayPort (eDP) Interface

| Standard                                       | Notes |

|------------------------------------------------|-------|

| VESA Embedded DisplayPort Standard Version 1.4 |       |

eDP is a mixed-signal interface consisting of four differential serial output lanes and one PLL. This PLL is used to generate a high frequency bit-clock from an input pixel clock enabling the ability to handle 10-bit parallel data per lane at the pixel rate for the desired mode. Embedded DisplayPort (eDP) modes (1.6 GHz for RBR; 2.16 GHz, 2.43 GHz, and 2.7 GHz for HBR; 3.24 GHz, 4.32 GHz, and 5.4 GHz for HBR2).

### Note

eDP has been tested according to DP1.2b PHY CTS even though eDPv1.4 supports lower swing voltages and additional intermediate bit rates. This means the following nominal voltage levels (400mV, 600mV, 800mV, 1200mV) and data rates (RBR, HBR, HBR2) are tested. This interface can be tuned to drive lower voltage swings below 400mV and can be programmed to other intermediate bit rates as per the requirements of the panel and the system designer.

The eDP block collects pixels from the output of the display pipeline, formats/encodes them to the eDP format, and then streams them to various output devices. It drives local panels only (does not support an external DP port), includes a small test pattern generator and CRC generator.

### **Features:**

- 1/2/4/ lane, single link

- additional link rates (2.16, 2.43, 3.24, 4.32 Gbps)

- · enhanced framing

- power sequencing

- reduced auxiliary timing

- reduced main voltage swing

- ASSR (alternate seed scrambler reset) for internal eDP panels

# 1.6 High Definition (HD) Audio/Video Subsystem

The HD Audio-Video Subsystem uses a collection of functional blocks to off-load audio and video processing activities from the CPU complex, resulting in fast, fully concurrent, highly efficient operation.

This subsystem is comprised of the following:

- (2x) Multi-Standard Video Decoder

- (2x) Multi-Standard Video Encoder

- JPG Processing Block

- Video Image Compositor (VIC)

- Audio Processing Engine (APE)

### 1.6.1 Multi-Standard Video Encoder

The JAX series module incorporates two instances of the NVIDIA Multi-Standard Video Encoder (NVENC). This multi-standard video encoder enables full hardware acceleration of various encoding standards. It performs high quality video encoding operations for mobile applications such as video recording and video conferencing. The encode processor is designed to be extremely power efficient without sacrificing performance.

Table 4 Supported Video Standards - Encode

| Standard     | Profile(s)                                    | Module        | Resolution (Maximum Number of Streams)            | Throughput (up to) |

|--------------|-----------------------------------------------|---------------|---------------------------------------------------|--------------------|

| H.265 (HEVC) | Main, Main10                                  | JAX, JAX 64GB | 4K60 (4)   4K30 (8)   1080p60 (16)   1080p30 (32) | (2x) 1000 MP/s     |

|              |                                               | JAXi          | 4K60 (2)   4K30 (6)   1080p60 (12)   1080p30 (24) | (2x) 800 MP/s      |

|              | Main 4:4:4, Main 4:4:4 10, MV (per view)      | JAX, JAX 64GB | 4K60 (2)   4K30 (4)   1080p60 (8)   1080p30 (16)  | (2x) 500 MP/s      |

|              |                                               | JAXi          | 4K30 (12)   1080p60 (6)   1080p30 (12)            | (2x) 400 MP/s      |

| H.264        | Baseline, Main, High                          | JAX, JAX 64GB | 4K60 (4)   4K30 (8)   1080p60 (14)   1080p30 (30) | (2x) 980 MP/s      |

|              |                                               | JAXi          | 4K60 (2)   4K30 (6)   1080p60 (12)   1080p30 (24) | (2x) 790 MP/s      |

|              | High 444, High 444 Predictive, MVC (per view) | JAX, JAX 64GB | 4K60 (2)   4K30 (4)   1080p60 (7)   1080p30 (15)  | (2x) 490 MP/s      |

| Standard | Profile(s) | Module Resolution (Maximum Number of Streams) |                                                   | Throughput (up to) |

|----------|------------|-----------------------------------------------|---------------------------------------------------|--------------------|

|          |            | JAXi                                          | 4K30 (2)   1080p60 (6)   1080p30 (12)             | (2x) 390 MP/s      |

| VP9      | profile 0  | JAX, JAX 64GB                                 | 4K60 (2)   4K30 (4)   1080p60 (10)   1080p30 (20) | (2x) 600 MP/s      |

|          |            | JAXi                                          | 4K60 (1)   4K30 (2)   1080p60 (6)   1080p30 (14)  | (2x) 480 MP/s      |

#### Note

Bitrate (up to): 15 Mbps for 1080p | 60 Mbps for 2160p Maximum throughput is half for YUV444 compared to YUV420.

A/V codec, post-processing and containers support are subject to software support; refer to NVIDIA software release notes for detailed specifications. Additional audio codecs may be supported using 3rd parties.

#### Features:

- Timestamp for Audio/Video Sync

- CBR and VBR rate control (supported in firmware)

- Programmable intra-refresh for error resiliency

- Macro-block based and bit based packetization (multiple slice)

- Motion estimation (ME) only mode

### 1.6.2 Multi-Standard Video Decoder

The JAX series module incorporates two instances of the NVIDIA Multi-Standard Video Decoder (NVDEC). This video decoder accelerates video decode, supporting low resolution mobile content, Standard Definition (SD), High Definition (HD) and UltraHD (8K, 4K, etc.) video profiles. The video decoder is designed to be extremely power efficient without sacrificing performance. The video decoder communicates with the memory controller through the video DMA which supports a variety of memory format output options. For low power operations, the video decoder can operate at the lowest possible frequency while maintaining real-time decoding using dynamic frequency scaling techniques.

Table 5 Supported Video Standards - Decode

| Standard     | Profile(s)                                | Module        | Resolution (Maximum Number of Streams)                           | Throughput (up to) |

|--------------|-------------------------------------------|---------------|------------------------------------------------------------------|--------------------|

| H.265 (HEVC) | Main, Main10                              | JAX, JAX 64GB | 8K30 (2)   4K60 (6)   4K30 (12)   1080p60 (26)  <br>1080p30 (52) | (2x) 1500 MP/s     |

|              |                                           | JAXi          | 8K30 (2)   4K60 (4)   4K30 (8)   1080p60 (18)  <br>1080p30 (36)  | (2x) 1200 MP/s     |

|              | Main 4:4:4, Main 4:4:4 10, MVC (per view) | JAX, JAX 64GB | 4K60 (2)   4K30 (6)   1080p60 (13)   1080p30 (26)                | (2x) 750 MP/s      |

|              |                                           | JAXi          | 4K60 (2)   4K30 (4)   1080p60 (8)   1080p30 (18)                 | (2x) 600 MP/s      |

| H.264        | Baseline, Main, High                      | JAX, JAX 64GB | 4K60 (4)   4K30 (8)   1080p60 (16)   1080p30 (32)                | (2x) 1000 MP/s     |

| Standard | Profile(s)                                    | Module        | Resolution (Maximum Number of Streams)            | Throughput (up to) |

|----------|-----------------------------------------------|---------------|---------------------------------------------------|--------------------|

|          |                                               | JAXi          | 4K60 (2)   4K30 (6)   1080p60 (12)   1080p30 (24) | (2x) 800 MP/s      |

|          | High 444, High 444 Predictive, MVC (per view) | JAX, JAX 64GB | 4K60 (2)   4K30 (4)   1080p60 (8)   1080p30 (16)  | (2x) 500 MP/s      |

|          |                                               | JAXi          | 4K30 (2)   1080p60 (6)   1080p30 (12)             | (2x) 400 MP/s      |

| VP9      | profile 0                                     | JAX, JAX 64GB | 4K60 (4)   4K30 (8)   1080p60 (19)   1080p30 (38) | (2x) 1000 MP/s     |

|          |                                               | JAXi          | 4K60 (2)   4K30 (6)   1080p60 (12)   1080p30 (24) | (2x) 800 MP/s      |

### Note

Bitrate (up to): 15 Mbps for 1080p | 60 Mbps for 2160p | 240 Mbps for 4320p

Maximum throughput is half for YUV444 compared to YUV420.

A/V codec, post-processing and containers support are subject to software support; refer to NVIDIA software release notes for detailed specifications. Additional audio codecs may be supported using 3rd parties.

# 1.6.3 JPEG Processing

The JPEG processing block is responsible for JPEG (de)compression calculations (based on JPEG still image standard), image scaling, decoding (YUV420, YUV422H/V, YUV444, YUV400) and color space conversion (RGB to YUV).

### Input (encode) formats:

• Pixel width: 8 bpc

Subsample format: YUV420Resolution (up to): 16K x 16K

Pixel pack format

Semi-planar/Planar for 420

# **Output (decode) formats:**

• Pixel width 8 bpc

• Resolution (up to): 16K x 16K

Pixel pack format

- Semi-planar/Planar for YUV420

- YUY2/Planar for 422H/422V

- Planar for YUV444/YUV400

- Interleaved RGBA

# 1.6.4 Video Image Compositor

The Video Image Compositor (VIC) implements various 2D image and video operations in a power-efficient manner. It handles various system UI scaling, blending, and rotation operations, video post-processing functions needed during video playback, and advanced de-noising functions used for camera capture.

- Color Decompression

- · High-quality De-interlacing

- Inverse Teleciné

- Temporal Noise Reduction

- New Bilateral Filter as spatial filter

- Improved TNR3 algorithm

- Scaling

- Color Conversion

- Memory Format Conversion

- Blend/Composite

- 2D Bit BLIT operation

- Rotation

- · Geometry transform processing

- Programmable 9-points controlled warp patch for distortion correction

- Real-time on-the-fly position generation from sparse warp map surface

- Pincushion/barrel/moustache distortion correction

- Distortion correction of 180 and 360 degree wide FOV lens

- Scene perspective orientation adjustment with IPT

- Full warp map capability

- Non-fixed Patch size with 4x4 regions

- External Mask bit map surface

# 1.6.5 Audio Processing Engine

The Audio Processing Engine (APE) is a self-contained unit with dedicated audio clocking that enables Ultra Low Power (ULP) audio processing. Software based post processing effects enable the ability to implement custom audio algorithms.

#### Features:

- 96 KB Audio RAM

- Low latency voice processing

- Audio Hub (AHUB)

- 4x (JAX), 3x (JAXi) I2S Stereo/TDM I/O

- DMIC.

- DSPK

- Multi-Channel IN/OUT

- Digital Audio Mixer: 10-in/5-out

- Up to eight channels per stream

- Simultaneous Multi-streams

- Flexible stream routing

- Multi-band Dynamic Range Compression (DRC)

- Up to three bands

- Customizable DRC curve with tunable knee points

- Up to 192 kHz, 32-bit sample, eight channels

- Parametric equalizer: up to 12 bands

- · Low latency sample rate conversion (SRC) and high quality asynchronous sample rate conversion (ASRC)

# 1.6.5.1 Inter-IC Sound (I2S) Controller

The Inter-IC Sound (I2S) controller implements full-duplex, bidirectional and single direction point-to-point serial interfaces. It can interface with I2S-compatible products, such as compact disc players, digital audio tape devices, digital sound processors, modems, Bluetooth chips, etc. The JAX series module supports I2S audio outputs with I2S/PCM interfaces supporting clock rates up to 24.576 MHz.

#### **Features:**

- Basic I2S modes supported (I2S, RJM, LJM, and DSP) in both Initiator and Target modes.

- PCM mode with short (one-bit-clock wide) and long-fsync (two bit-clocks wide) in both Initiator and Target modes.

- Network (Telephony) mode with independent slot-selection for both Tx and Rx

- TDM mode with flexibility in number of slots and slot(s) selection.

- Capability to drive-out a High-z outside the prescribed slot for transmission

- Flow control for the external input/output stream.

### Table 6 TDM Timing Parameters (Initiator Mode)

| Symbol            | Parameter            | Min                | Тур | Max    | Unit | Notes |

|-------------------|----------------------|--------------------|-----|--------|------|-------|

| F <sub>SCK</sub>  | Frequency            |                    |     | 24.576 | MHz  |       |

| T <sub>CYL</sub>  | I2Sx_SCLK cycle time | 1/F <sub>SCK</sub> |     |        | ns   |       |

| T <sub>FDLY</sub> | I2Sx_LRCK delay      | 0                  |     | 4.5    | ns   |       |

| Symbol            | Parameter            | Min                    | Тур | Мах                   | Unit | Notes |

|-------------------|----------------------|------------------------|-----|-----------------------|------|-------|

| t <sub>DDLY</sub> | I2Sx_SDOUT delay     | 0                      |     | 4.5                   | ns   |       |

| t <sub>DSU</sub>  | I2Sx_SDIN setup time | 2                      | -   | -                     | ns   |       |

| t <sub>DH</sub>   | I2Sx_SDIN hold time  | 2                      | -   | -                     | ns   |       |

| t <sub>RT</sub>   | I2Sx_SCLK rise time  |                        |     | 5% * T <sub>CYL</sub> |      |       |

| t <sub>FT</sub>   | I2Sx_SCLK fall time  |                        |     | 5% * T <sub>CYL</sub> |      |       |

| t <sub>CH</sub>   | I2Sx_SCLK high time  | 45% * T <sub>CYL</sub> |     |                       |      |       |

| t <sub>CL</sub>   | I2Sx_SCLK low time   | 45% * T <sub>CYL</sub> |     |                       |      |       |

# Table 7 TDM Timing Parameters (Target Mode up to 24.576 MHz)

| Symbol            | Parameter            | Min                      | Тур | Max                        | Unit | Notes |

|-------------------|----------------------|--------------------------|-----|----------------------------|------|-------|

| F <sub>SCK</sub>  | Frequency            |                          |     | 24.576                     | MHz  |       |

| T <sub>CYL</sub>  | I2Sx_SCLK cycle time | 1/F <sub>SCK</sub>       |     |                            | ns   |       |

| t <sub>DDLY</sub> | I2Sx_SDOUT delay     | 0                        |     | 4.5                        | ns   |       |

| t <sub>DSU</sub>  | I2Sx_SDIN setup time | 2                        | -   | -                          | ns   |       |

| t <sub>DH</sub>   | I2Sx_SDIN hold time  | 2                        |     |                            | ns   |       |

| t <sub>FSU</sub>  | I2Sx_LRCK setup      | 2                        |     | 45% * T <sub>CYL</sub> - 2 | ns   | 1     |

| t <sub>FSH</sub>  | I2Sx_LRCK hold       | 55% T <sub>CYL</sub> + 2 |     |                            | ns   | 2     |

| t <sub>RT</sub>   | I2Sx_SCLK rise time  |                          |     | 5% * T <sub>CYL</sub>      |      |       |

| t <sub>FT</sub>   | I2Sx_SCLK fall time  |                          |     | 5% * T <sub>CYL</sub>      |      |       |

| t <sub>CH</sub>   | I2Sx_SCLK high time  | 45% * T <sub>CYL</sub>   |     |                            |      |       |

| t <sub>CL</sub>   | I2Sx_SCLK low time   | 45% * T <sub>CYL</sub>   |     |                            |      |       |

1. Max  $t_{\mathsf{FSU}}$  requirement only applies while Fsync Launching on Clock Raising Edge

2. Min  $t_{FSH}$  (55%  $T_{CYL}$  + 2) requirement only applies while Fsync Launching on Clock Raising Edge; in other use cases, Min  $t_{FSH}$  is 2ns.

Table 8 TDM Timing Parameters (Target Mode up to 12.288 MHz)

| Symbol            | Parameter            | Min          | Тур | Мах            | Unit | Notes |

|-------------------|----------------------|--------------|-----|----------------|------|-------|

| F <sub>SCK</sub>  | Frequency            |              |     | 12.288         | MHz  |       |

| T <sub>CYL</sub>  | I2Sx_SCLK cycle time | 1/Fsck       |     |                | ns   |       |

| t <sub>DDLY</sub> | I2Sx_SDOUT delay     | 0            |     | 4.5            | ns   |       |

| t <sub>DSU</sub>  | I2Sx_SDIN setup time | 2            | -   | -              | ns   |       |

| t <sub>DH</sub>   | I2Sx_SDIN hold time  | 2            |     |                | ns   |       |

| t <sub>FSU</sub>  | I2Sx_LRCK setup      | 2            |     | 35% * TCYL - 2 | ns   | 1     |

| t <sub>FSH</sub>  | I2Sx_LRCK hold       | 65% TCYL + 2 |     |                | ns   | 2     |

| t <sub>RT</sub>   | I2Sx_SCLK rise time  |              |     | 15%* TCYL      |      |       |

| t <sub>FT</sub>   | I2Sx_SCLK fall time  |              |     | 15%* TCYL      |      |       |

| t <sub>CH</sub>   | I2Sx_SCLK high time  | 35% * TCYL   |     |                |      |       |

| t <sub>CL</sub>   | I2Sx_SCLK low time   | 35% * TCYL   |     |                |      |       |

- 1. Max t<sub>FSU</sub> requirement only applies while Fsync Launching on Clock Raising Edge

- 2. Min  $t_{FSH}$  (35%  $T_{CYL}$  + 2) requirement only applies while Fsync Launching on Clock Raising Edge; in other use cases, Min  $t_{FSH}$  is 2ns.

# 1.6.5.2 Digital MIC Controller (DMIC)

The DMIC Controller is used to interface with PDM base input devices. The DMIC controller converts Pulse Density Modulation (PDM) signals to Pulse Code Modulation (PCM) signals.

### **Features:**

Sample rate support: 8 kHz - 48 kHz

Input PCM bit width: 16 - 24 bits

• Oversampling Ratio: 64, 128, 256

# 1.6.5.3 Digital Speaker Controller (DSPK)

The PDM transmit block converts multi-bit PCM audio input to oversampled 1-bit PDM output. The mono or stereo audio is transmitted over a data/clock pair (I<sup>2</sup>S interface) to an external codec. The block consists of an interpolator followed by a Delta Sigma Modulator (DSM).

- Sample rate support: 8 48 kHz

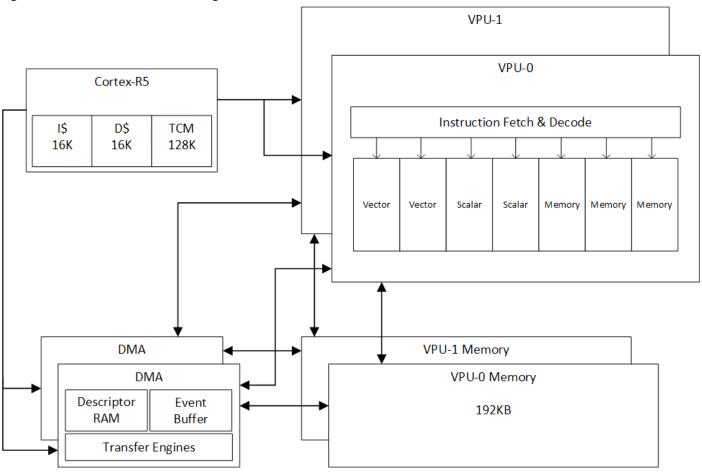

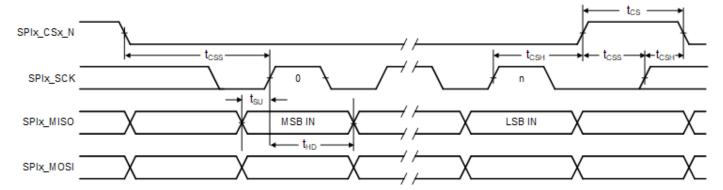

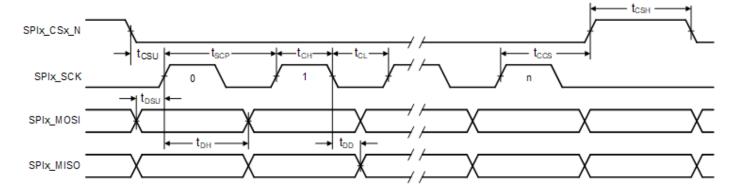

- Input PCM bit-width: 16 24 bits